Interrupts

- Instead of having to constantly poll to see if a flag is set, interrupt the processor when a flag is set

- When a peripheral needs an action, it can generate an interrupt

Handling

- Masks and priority are to determine which interrupts should interrupt other interrupts

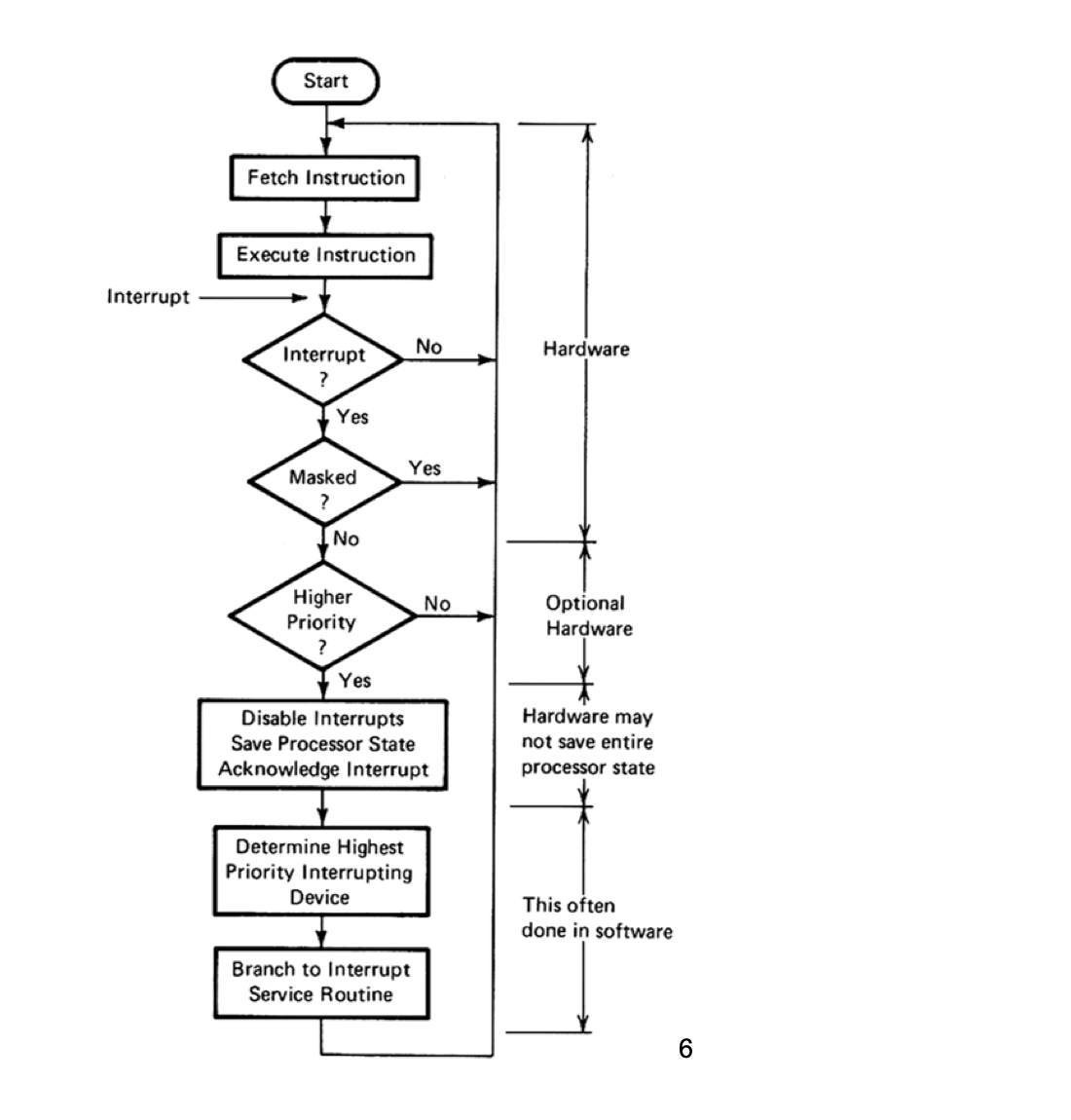

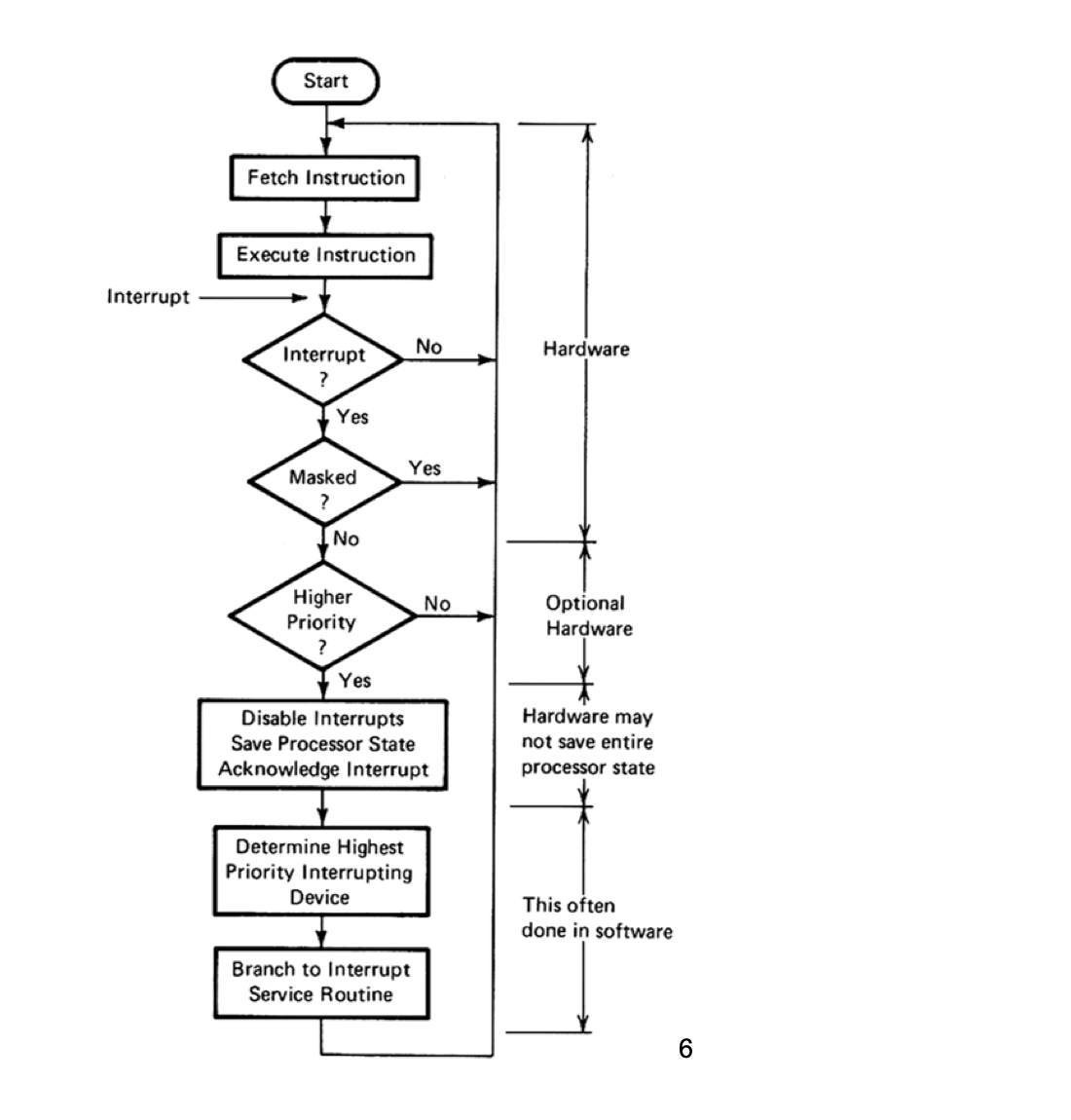

- On Interrupt

- Check if it should interrupt

- The uP will complete execution of the current instruction

- Save the processor status (the CPU registers, except the stack pointer) on the stack

- Branch to a special location (interrupt vector address) to execute a interrupt service routine (ISR) that will service the interrupting

Implementation

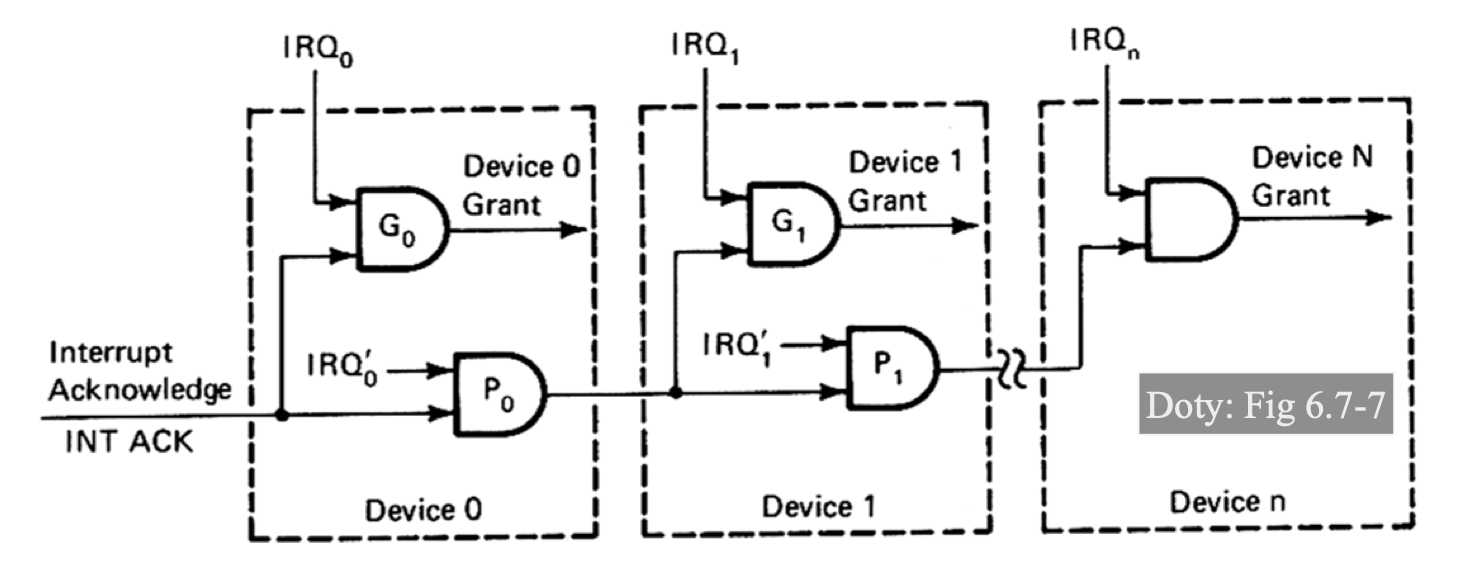

- Polling: Daisy-Chain

- Finding ISR Address

In XMEGA

- Has a programmable multilevel interrupt control (PMIC)

- Has 3 interrupt levels (low, medium, high)

- Within each level, the interrupt priority is based on the interrupt vector address (lower the address, higher the priority)

- Interrupts have a global enable (bit

I in status register)

- Set and cleared by

SEI and CLI

RETI (interrupt return) must exist at the end of each interrupt service routine- All interrupts have an interrupt associated flag

- When the interrupt condition is set, the interrupt flag will be set even if the corresponding interrupt is not enabled

- For some interrupts, the interrupt flag is automatically cleared when handled

- Should just always clear just in case

- Clear by running a 1 to it

- Does not support interrupting interrupts

- A higher priority interrupt will just run right after the current interrupt finishes

- NOTE: XMEGA does not store the status register (

SREG) for some reason so it almost always has to be manually pushed and popped