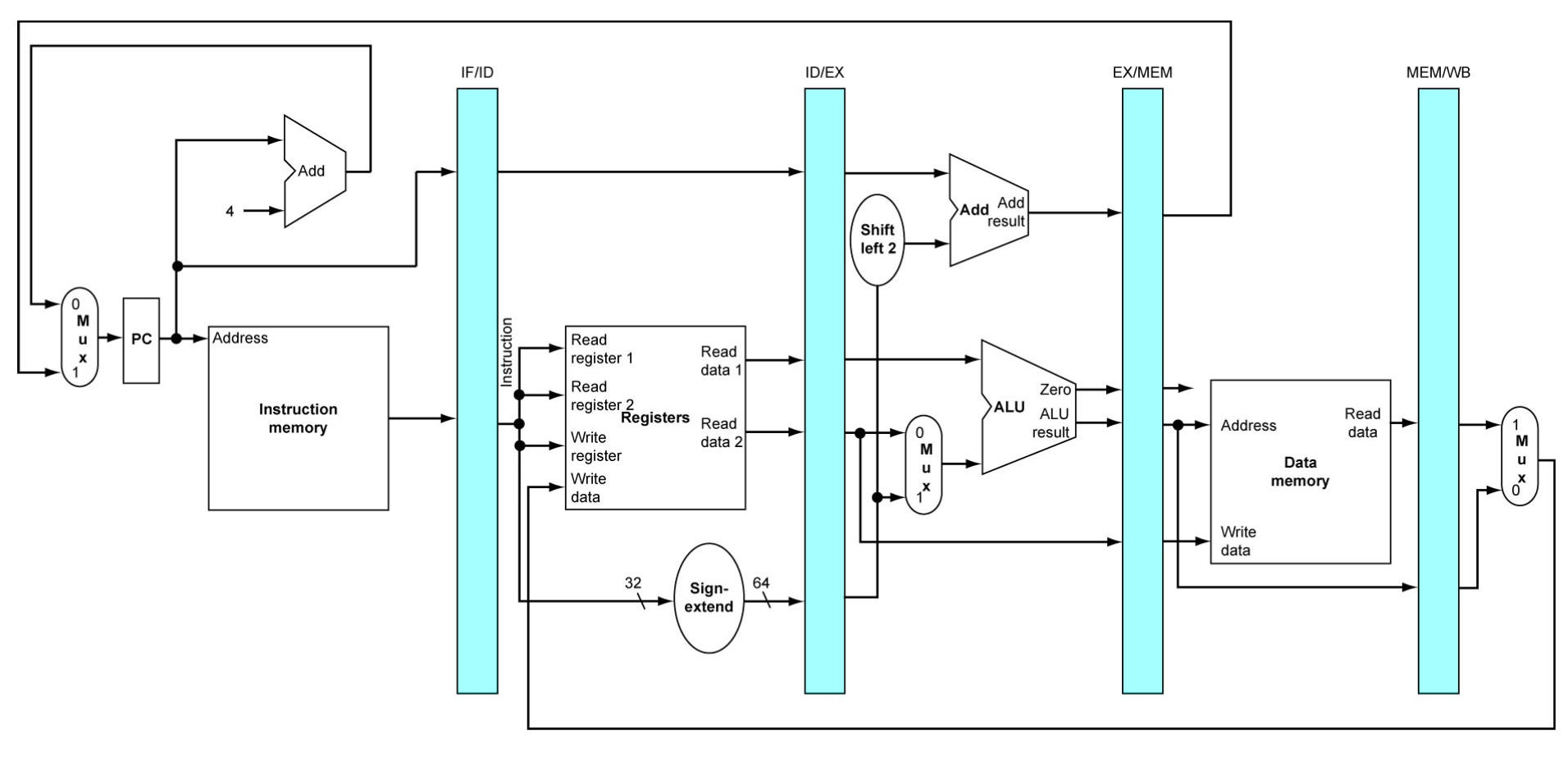

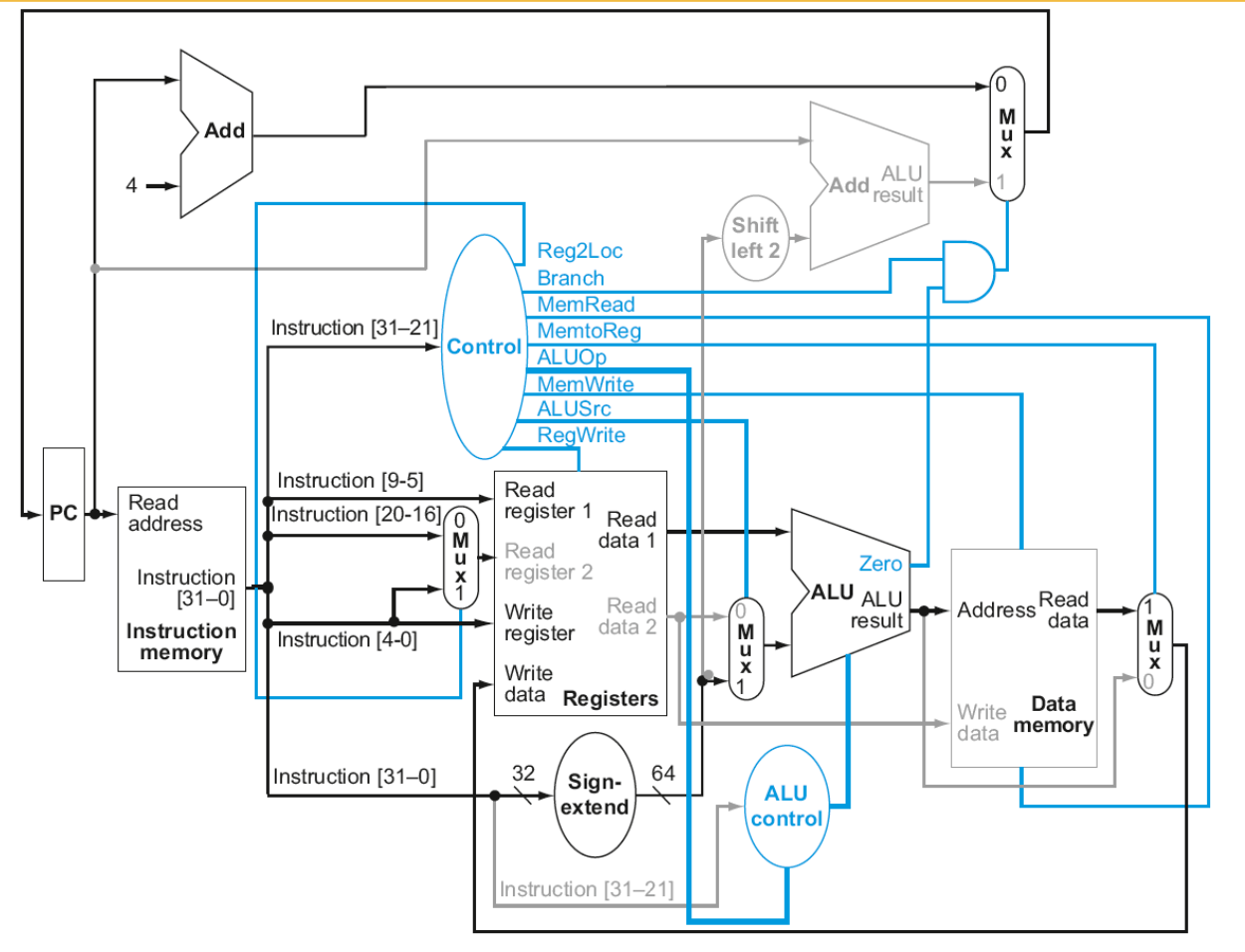

Datapath

- Elements that process data and addresses in the CPU

- Registers, ALUs, MUXs, Memories

- Part of The Processor

- Reads and acts on LEGv8 Machine Code

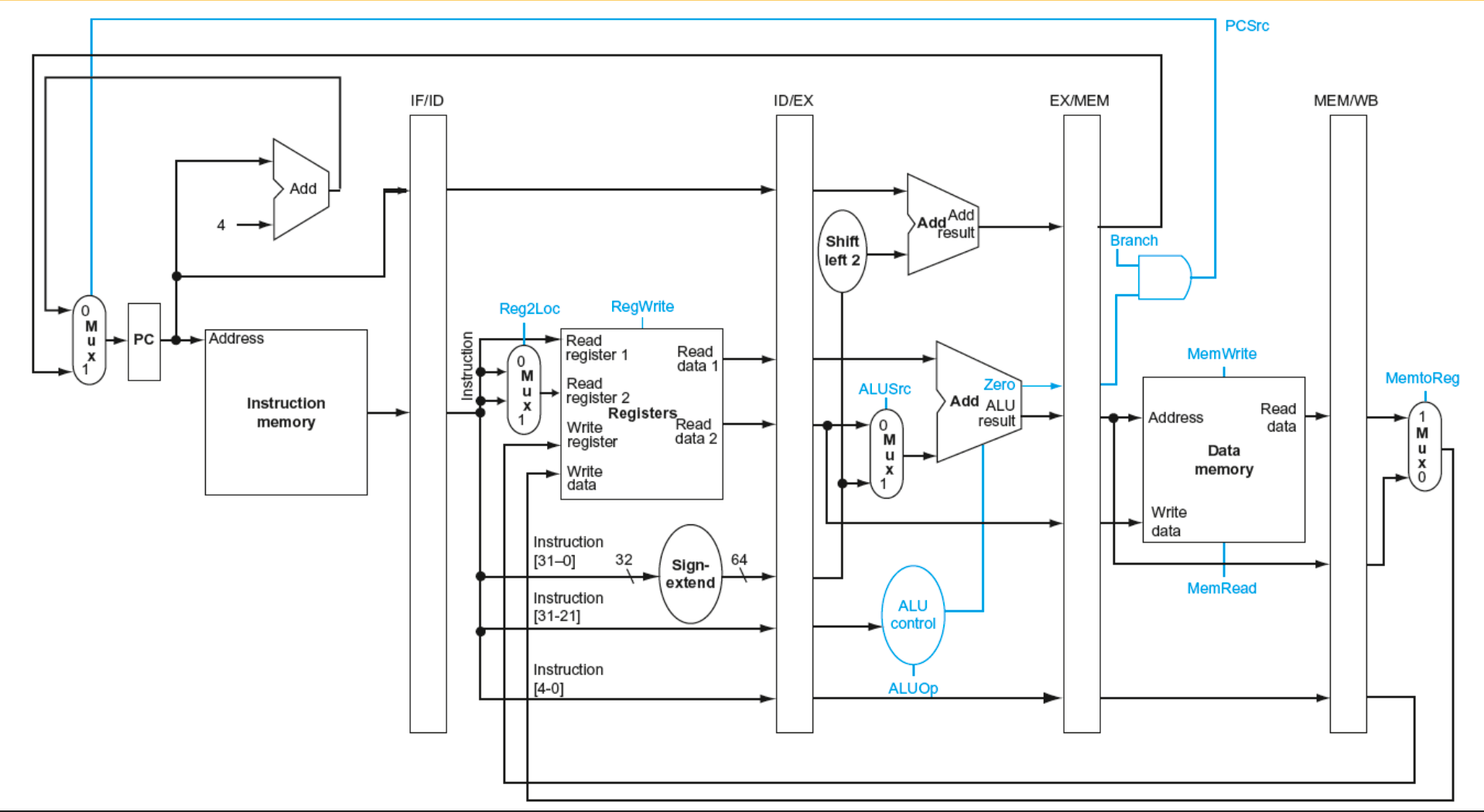

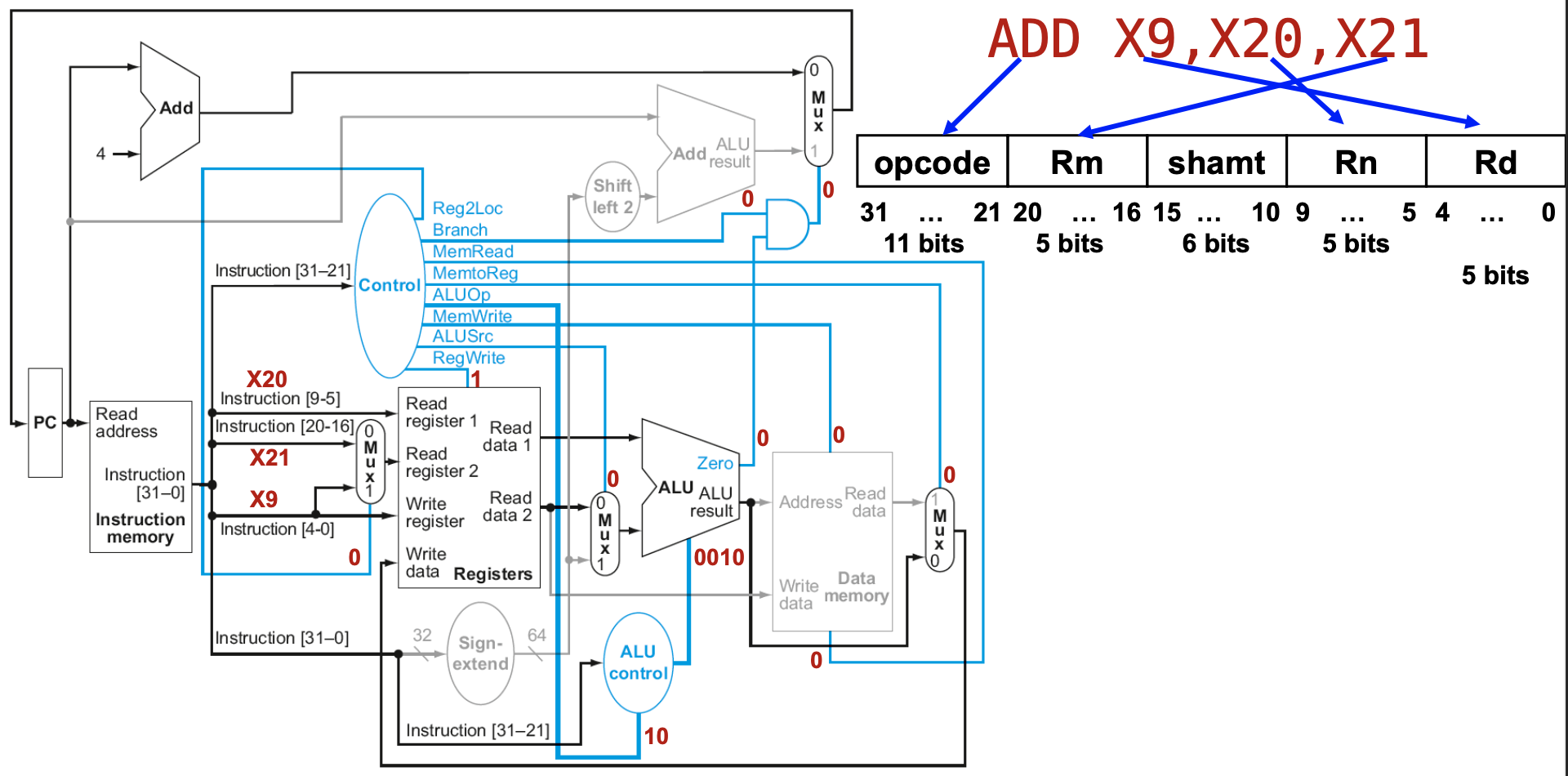

Components

- The blue lines are what connects to the Control

- A lot of there instructions will take multiple clock cycles, but the control will take care of that by not sending the read and write signals until it is time

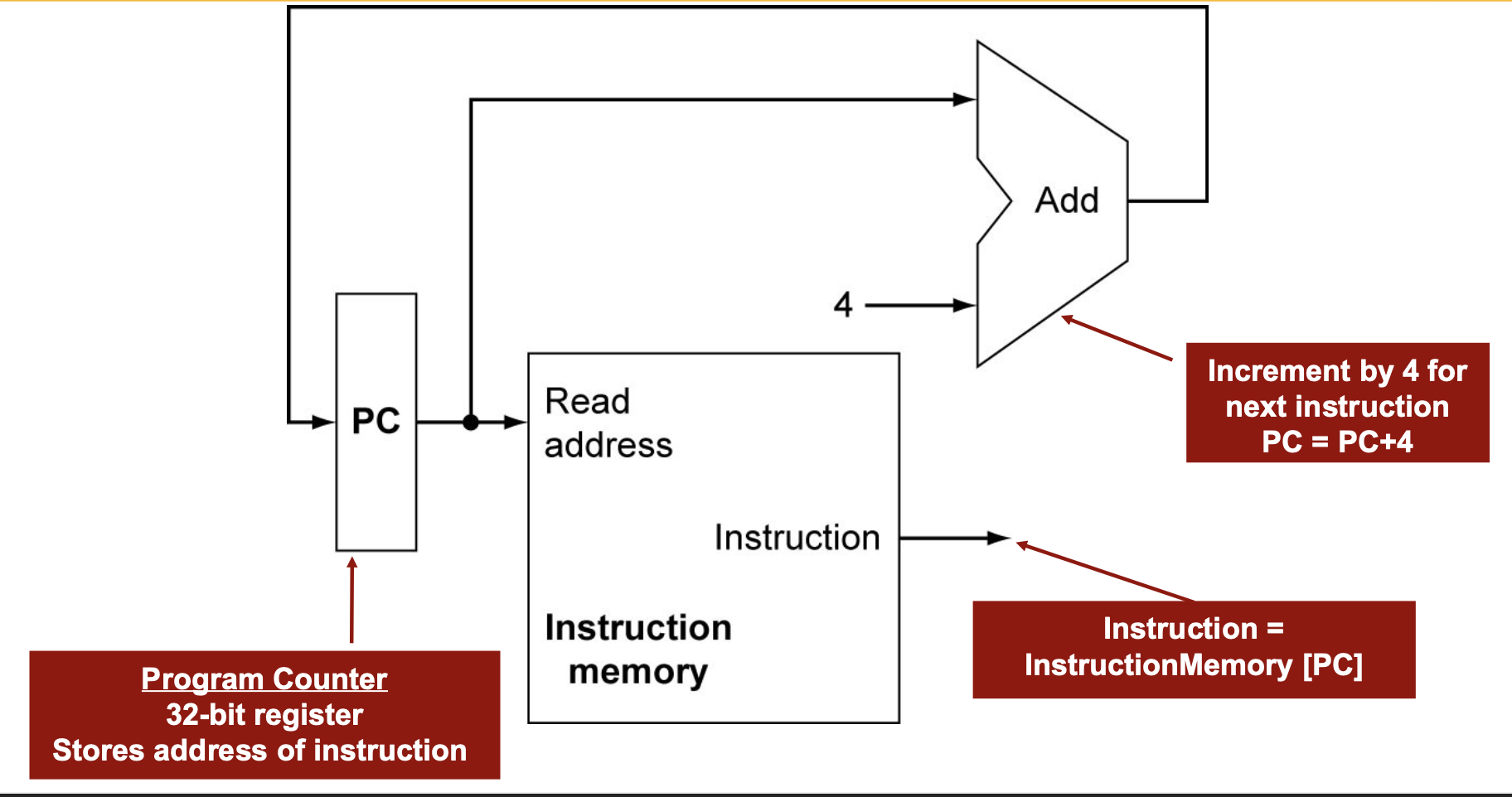

Instruction Fetch

- Instruction memory is stored separately from data memory and is read only

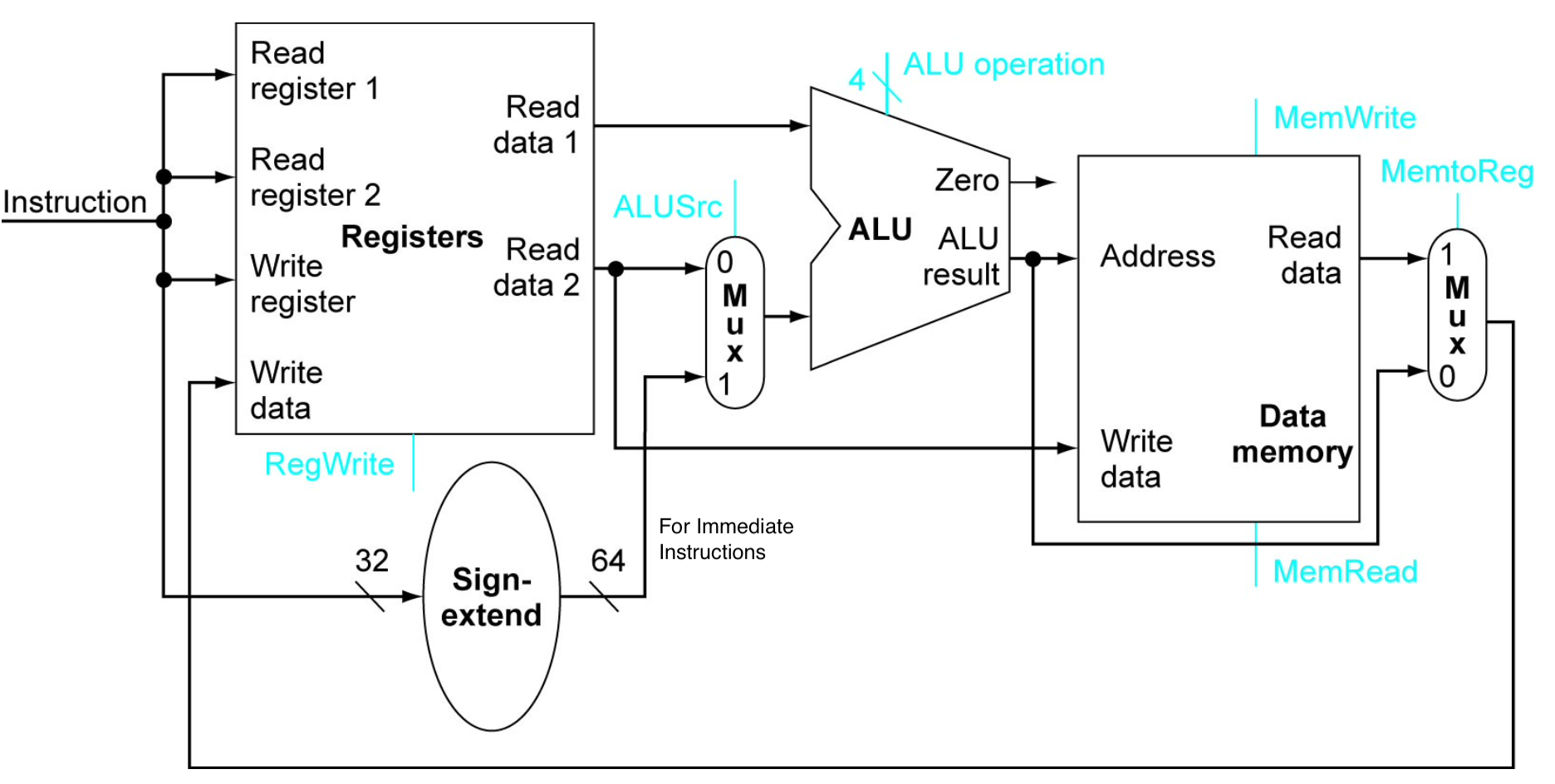

R and D Format

- R Steps

- Read two register operands

- Perform arithmetic/logical operation

- Write register result

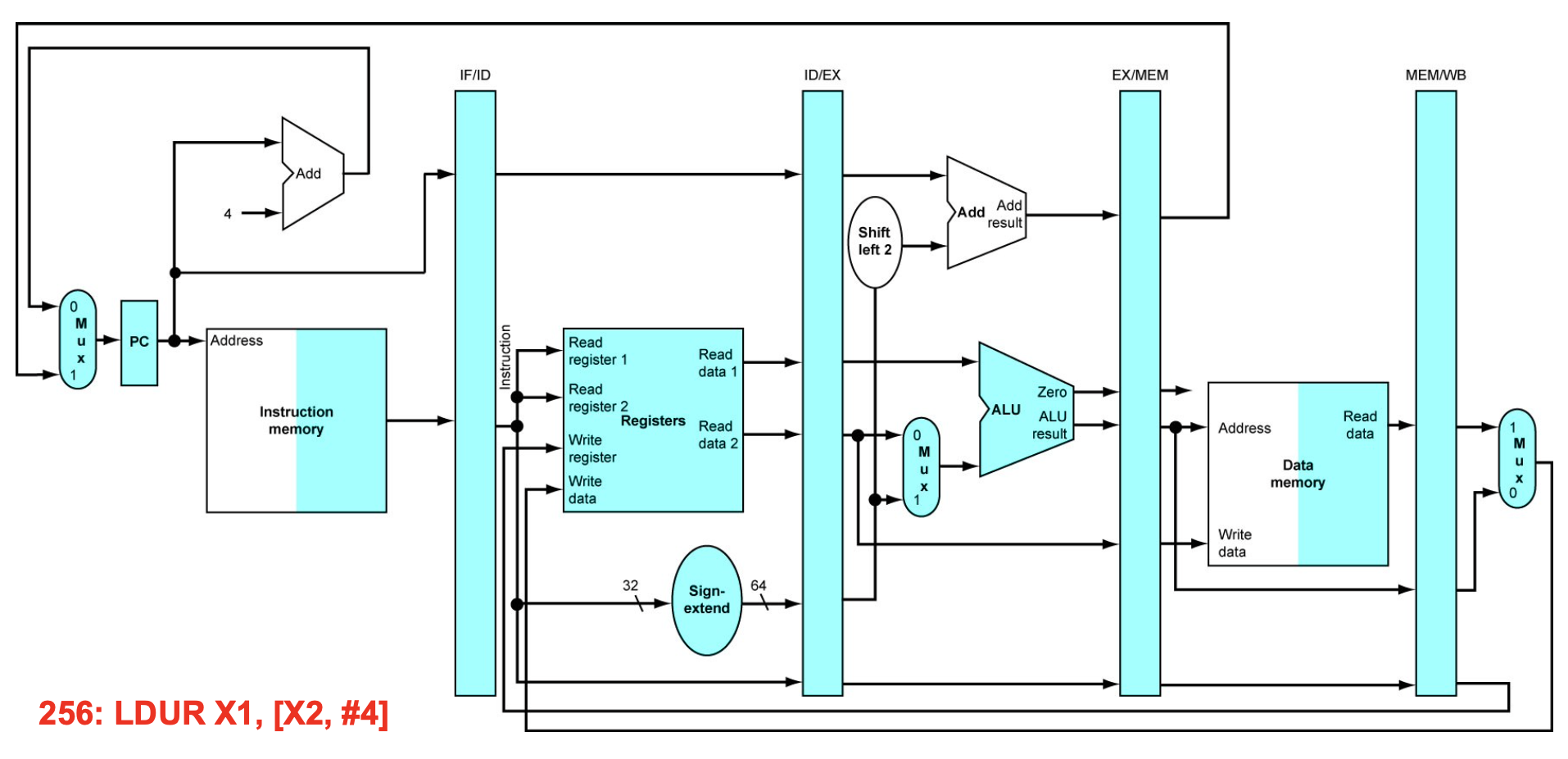

- D Steps

- Read register operands

- Calculate address using 32-bit offset (Use ALU, but sign-extend offset)

- Load: Read memory and update register, Store: Write register value to memory

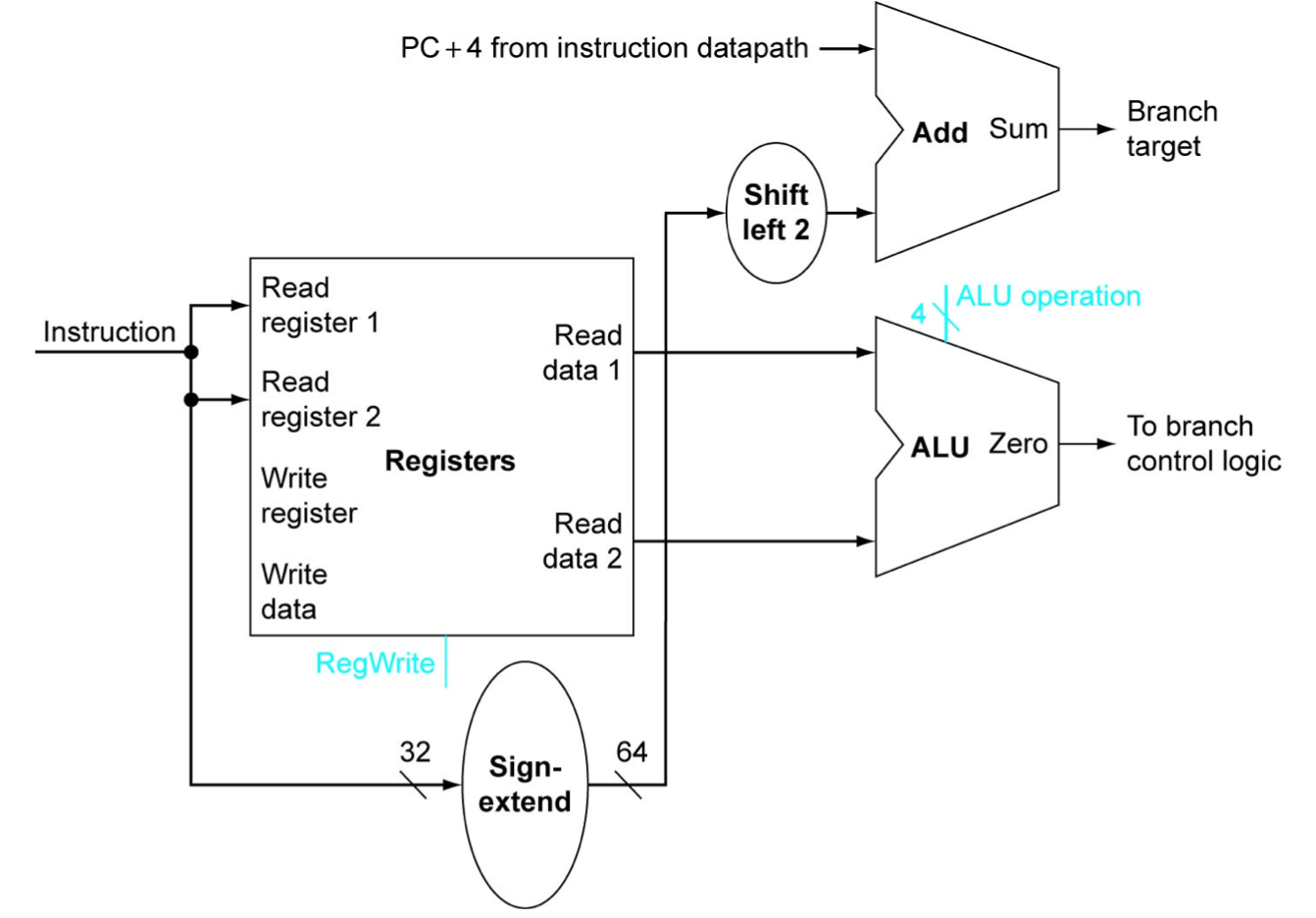

B and CB

- Steps

- Read register operands

- Compare operands (Use ALU, subtract and check Zero output)

- Calculate target address

- Sign-extend displacement

- Shift left 2 places (word displacement)

- Add to PC + 4 (Already calculated by instruction fetch)

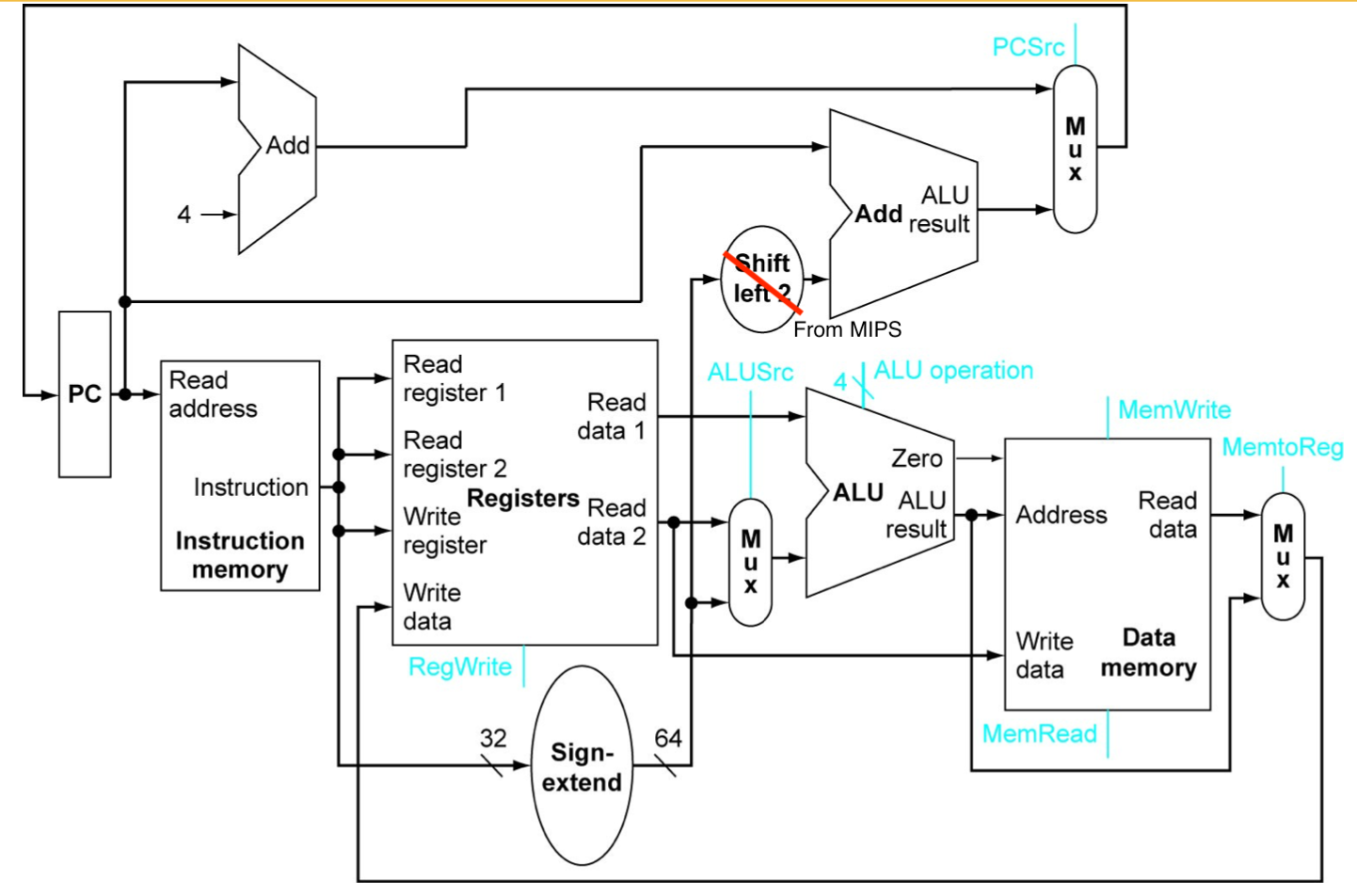

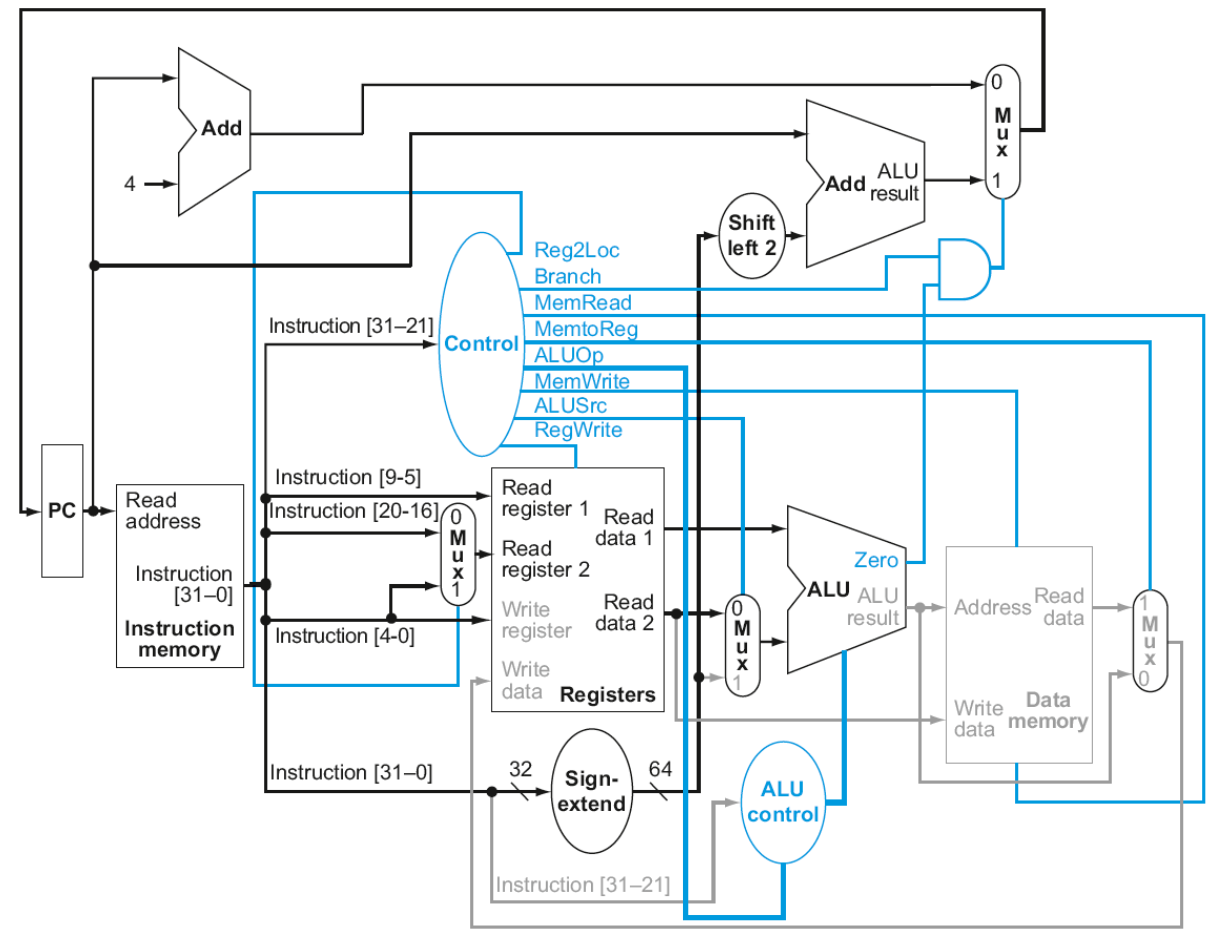

Full Datapath

Tracings

- R Instruction:

- Load instruction:

- Conditional branch:

- Unconditional branch:

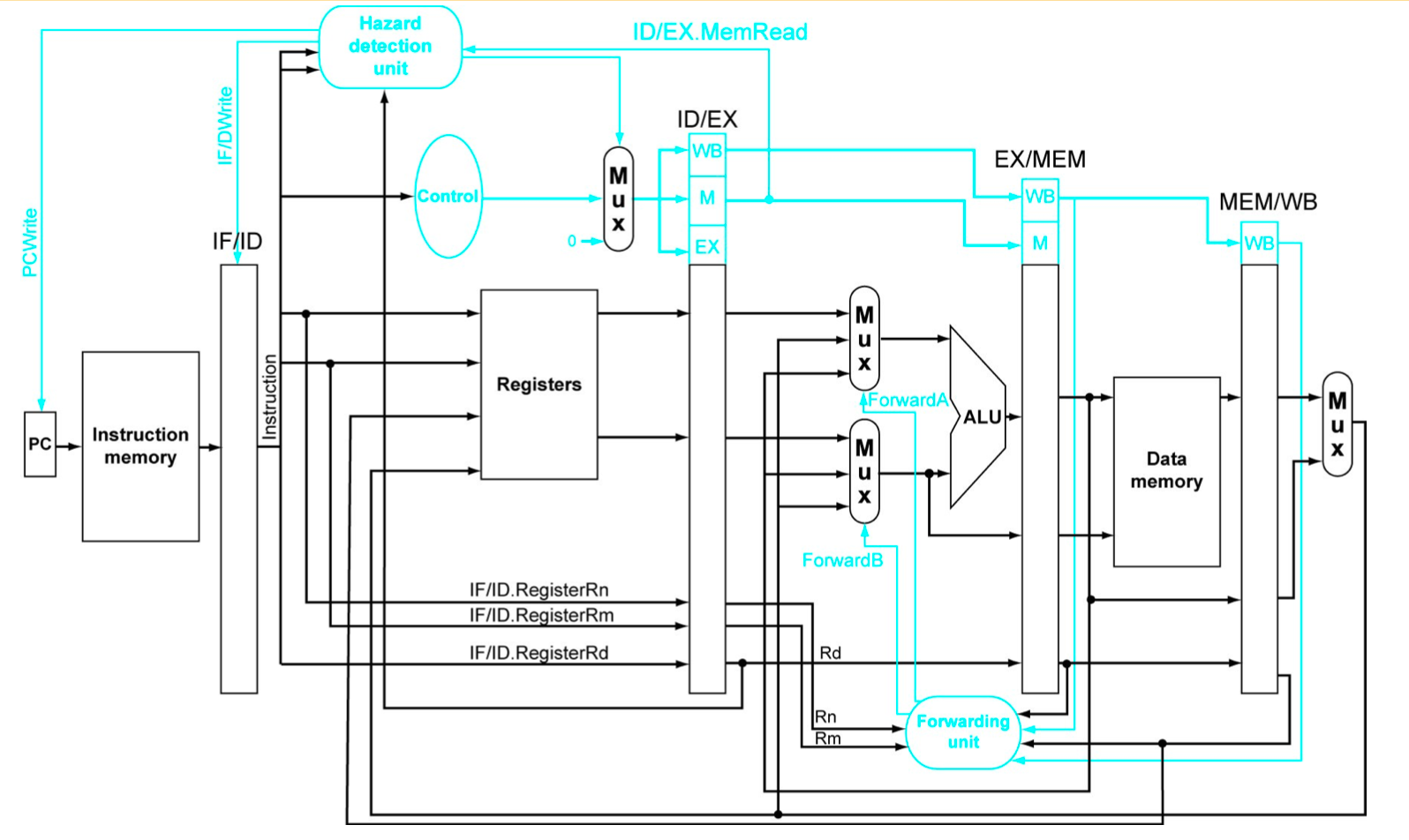

Pipelining

- Performance is improved using Pipelining

- Implementation

- When used by load

- Additionally carries the write register with it because it needs to write after the memory is retrieved/values is computed in a stage after the initial register access stage

- Pipelined datapath with Control Signals

- Pipelined datapath with forwarding and stalling

- There is a limited number of forwarding paths able to be added, so they are tested to see which ones are the most important to add