LEGv8 Machine Code

- Encoded as 32-bit instruction words

- All operands are registers

- Format

- Opcode: 11 bits

- Second Register (Rm): 5 bits

- Shift amount (shamt): 6 bits

- First register (Rn): 5 bits

- Destination (Rd): 5 bits

- Rd = Rn OP (Rm << shamt)

- One operand is an immediate value

- Format

- Opcode: 10 bits

- Immediate: 12 bits (zero extended)

- Input Register (Rn): 5 bits

- Destination Register (Rd): 5 bits

- Load/Store

- Format

- Opcode: 11 bits

- Address (constant offset): 9 bits

- Op2: 2 bits

- Base Register (Rn): 5bits

- Destination or source register (Rt): 5 bits

- Conditional branch

- Format

- Opcode: 8 bits

- Location: 19 bits (PC-relative)

- Stores the number of words to the next instruction (instead of bytes) since all instructions are that long

- In two’s complement form to allow for going backwards (#question confirm this)

- Condition Register: 5 bits

- Unconditional branch (jump)

- Format

- Opcode: 6 bits

- Location: 26 bits (PC-relative)

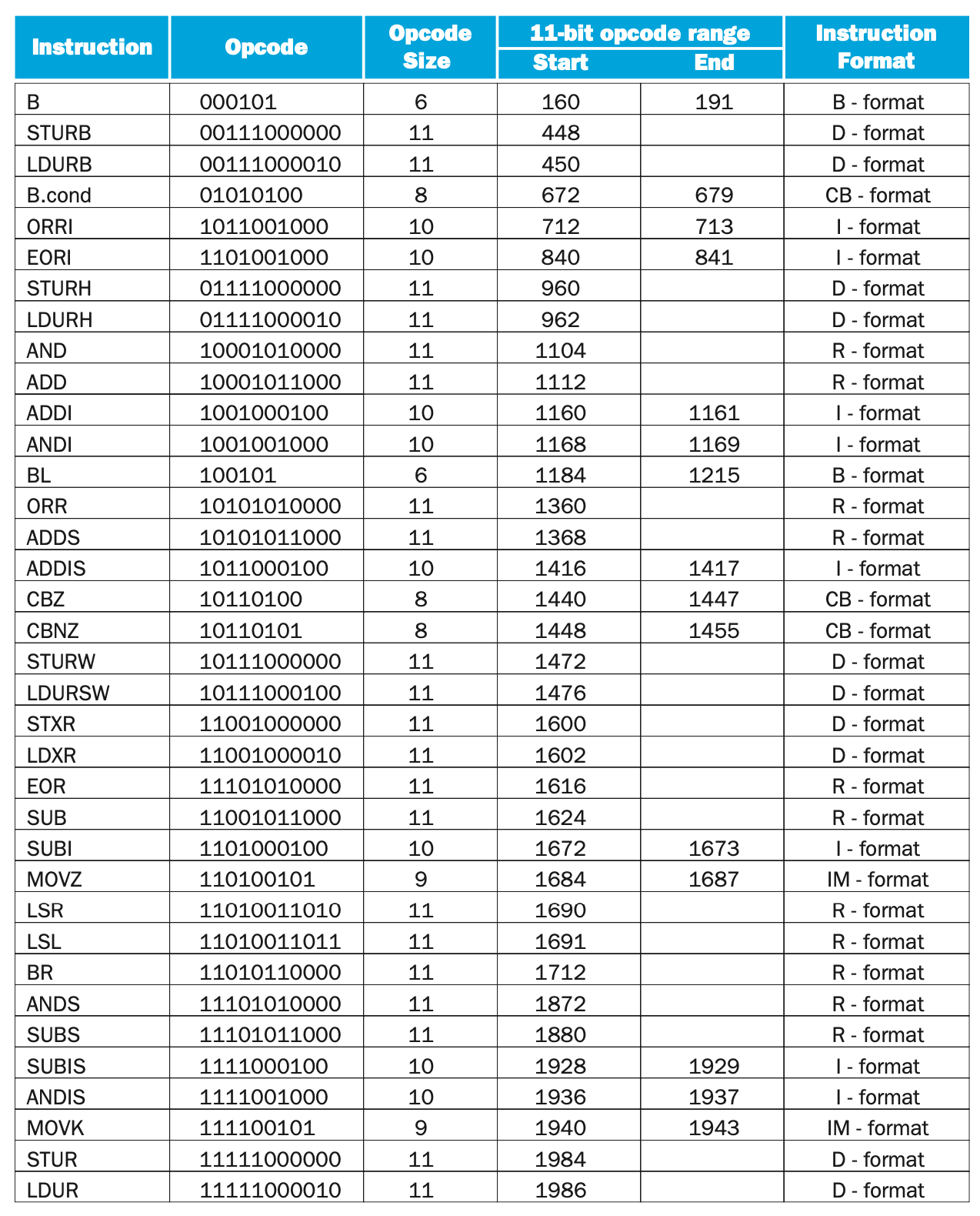

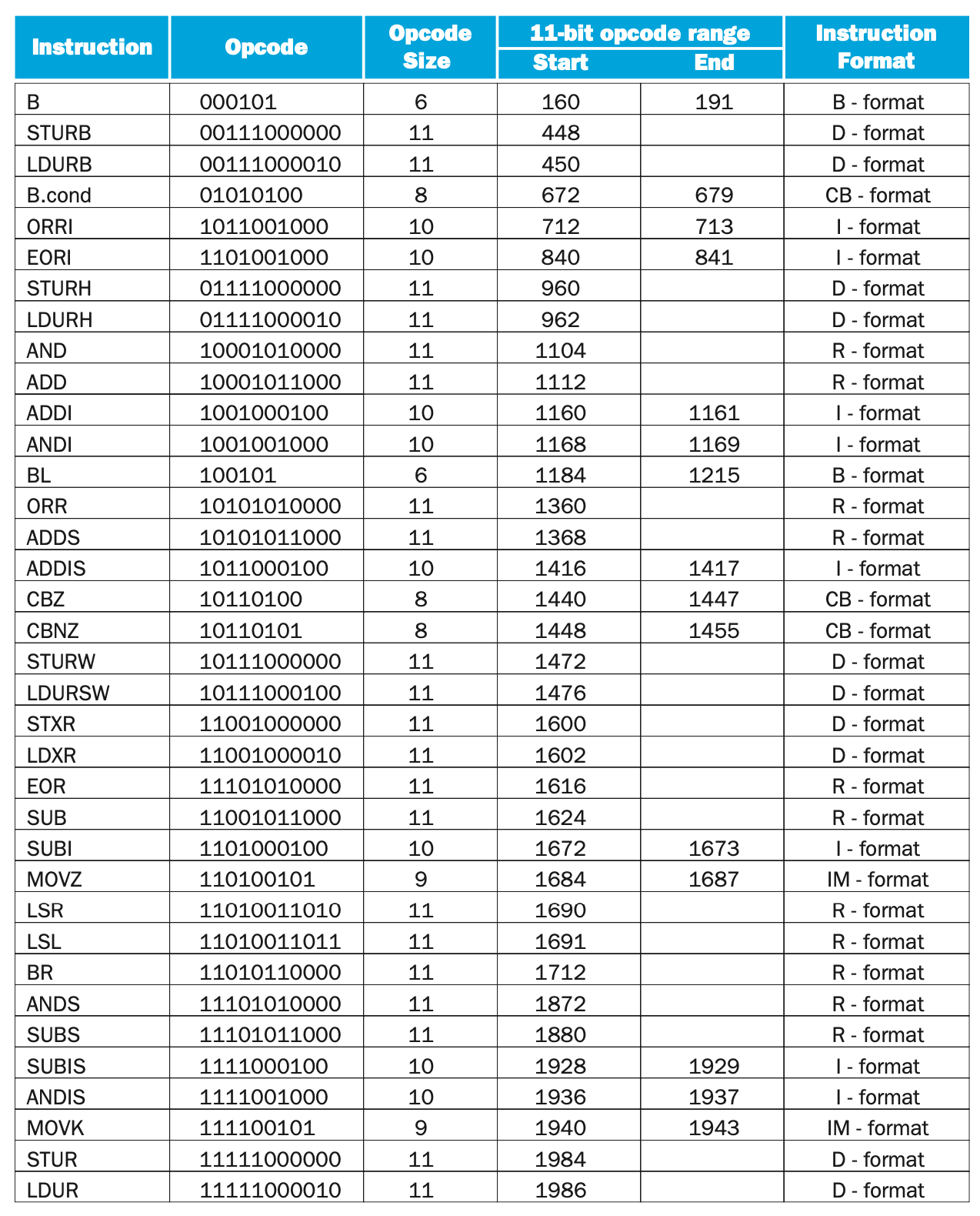

Opcodes